소자 공부 로드맵

소자 공부는 전기적 동작 → 구조 → 공정/재료 → 시스템 연결 순으로 접근하면 이해가 빠릅니다. 이 페이지는 그 순서를 따라가며 핵심 개념을 연결합니다.

1단계: PN 접합과 기본 소자

섹션 제목: “1단계: PN 접합과 기본 소자”- PN 접합의 공핍층/전기장과 다이오드 동작

- 캐패시터의 축전 원리와 누설 메커니즘

- 온도/결함/도핑이 전기적 특성에 미치는 영향

이 단계의 목표는 “전하 분포가 전기적 특성을 바꾼다”는 감각을 잡는 것입니다.

2단계: MOSFET 구조와 동작

섹션 제목: “2단계: MOSFET 구조와 동작”- 게이트 전압으로 채널을 형성하고 전류를 제어

- Vt/SS/Id가 속도·전력·누설과 연결

- 짧은 채널 효과와 스케일링 한계 이해

MOSFET의 성능은 결국 게이트가 채널을 얼마나 잘 제어하느냐에 달려 있습니다.

3단계: 메모리 소자(집적도 vs 신뢰성)

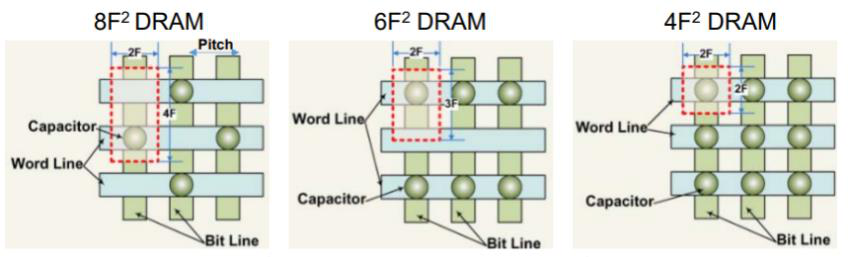

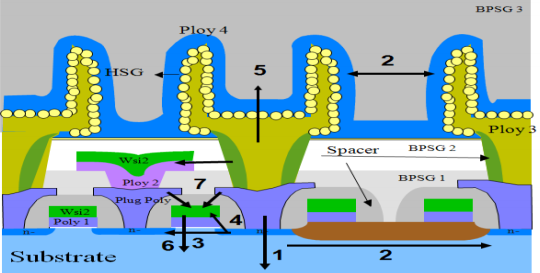

섹션 제목: “3단계: 메모리 소자(집적도 vs 신뢰성)”DRAM은 1T1C 구조를 기반으로 집적도를 끌어올리는 과정이고,

NAND는 3D 적층과 셀 구조 최적화로 용량을 확장합니다.

이 단계의 핵심은 셀 구조 변화가 신뢰성/수율/전력에 어떤 대가를 요구하는지 파악하는 것입니다.

4단계: 재료·공정과 소자 특성의 연결

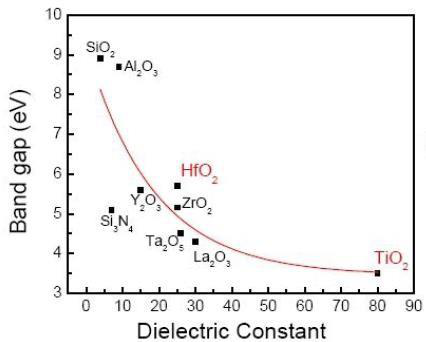

섹션 제목: “4단계: 재료·공정과 소자 특성의 연결”소자 특성은 **재료 물성(유전율/밴드갭)**과 공정 조건(산화막, 금속 게이트, 계면 품질)에 의해 크게 달라집니다.

고유전율(High‑k)은 누설을 줄이고 Vt를 제어하는 데 유리하지만,

재료 선택에 따라 계면 결함/신뢰성 이슈가 발생할 수 있습니다.

5단계: 패키징·시스템 연결(2.5D/3D)

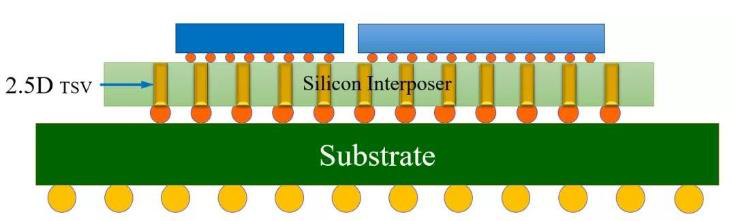

섹션 제목: “5단계: 패키징·시스템 연결(2.5D/3D)”최근에는 소자 자체뿐 아니라 칩렛/인터포저/3D 적층 같은 패키징이 성능을 결정합니다.

소자 공부는 결국 시스템까지 연결되어야 완성됩니다.

메모리-로직 연결과 패키징 열/신호 무결성까지 생각하는 시각이 중요합니다.

더 공부하기

섹션 제목: “더 공부하기”- Intel Foundry: Intel 18A (RibbonFET/PowerVia)

https://www.intel.com/content/www/us/en/foundry/process/18a.html - Micron: 1γ(1‑gamma) DRAM 샘플 출하 보도자료

https://investors.micron.com/news-releases/news-release-details/micron-announces-shipment-1g-1-gamma-dram-pioneering-memory - TSMC: Advanced Packaging Services (CoWoS/InFO/SoIC)

https://www.tsmc.com/english/dedicatedFoundry/services/advanced-packaging - Samsung Foundry: Advanced Package

https://semiconductor.samsung.com/foundry/advanced-package/ - JEDEC: HBM3 표준 발표(보도자료)

https://www.businesswire.com/news/home/20220127005320/en/JEDEC-Publishes-HBM3-Update-to-High-Bandwidth-Memory-HBM-Standard - imec: 3D Integration Research

https://www.imec-int.com/en/expertise/cmos-advanced/connect/3d-integration - Stanford Nanofabrication Facility (SNF)

https://snf.stanford.edu/ - ASML: EUV Lithography Systems Overview

https://www.asml.com/en/en/products/euv-lithography-systems - SEMI: Overview of Semiconductor Manufacturing

https://www.semi.org/en/event/overview-semiconductor-manufacturing - MIT OCW 6.720J: Integrated Microelectronic Devices

https://ocw.mit.edu/courses/6-720j-integrated-microelectronic-devices-spring-2007/