WaferWiki

WaferWiki는 반도체를 공부/취업/연구/투자하려는 사람을 위한 지식베이스입니다. 각 페이지는 한 번에 읽히는 분량과 핵심 그림/도식을 함께 제공합니다.

빠른 시작

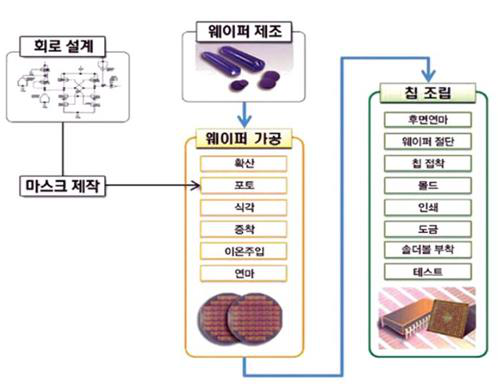

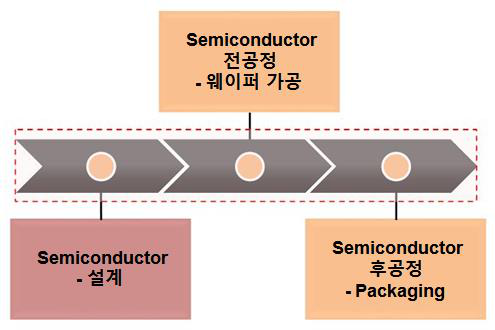

섹션 제목: “빠른 시작”- 공정 흐름을 먼저 잡고 싶다면: 기술/공정 허브

- 소재/장비를 연결해 보고 싶다면: 소재/장비 허브

- 산업 구조/시장 용어가 궁금하다면: 기업/시장 허브

학생 중심으로 구성

섹션 제목: “학생 중심으로 구성”- 학부생/대학원생: 빠른 개념 정리와 참고 이미지

- 취준생: 직무별 로드맵과 준비 방향

- 연구자/투자자: 산업 구조/시장 흐름 정리

앞으로 추가될 것

섹션 제목: “앞으로 추가될 것”- 뉴스/이슈 큐레이션

- 커뮤니티/Q&A

- 채용/교육 정보

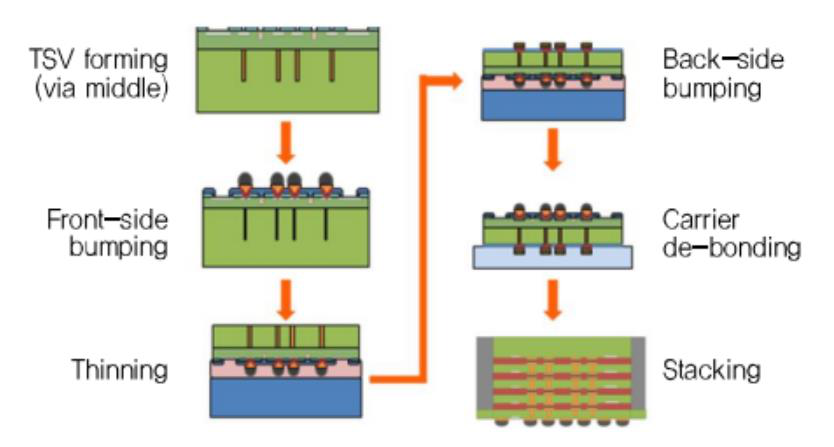

패키징/적층 예시

섹션 제목: “패키징/적층 예시”TSV와 마이크로범프는 고대역폭 메모리(HBM) 같은 적층 패키징의 핵심 구조입니다.

다이 적층, 본딩, 범프 형성 등은 “후공정”에서 성능을 좌우합니다.

사용 원칙

섹션 제목: “사용 원칙”- 핵심 개념을 먼저, 세부는 링크로 확장

- 공정/소자/시장 간 연결성 강조

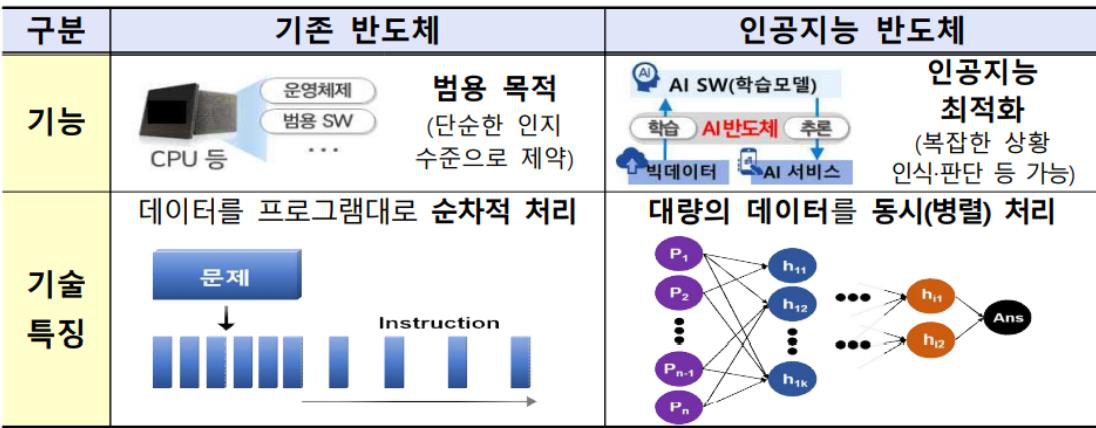

AI 반도체 흐름 변화

섹션 제목: “AI 반도체 흐름 변화”AI 워크로드는 연산 병렬성과 메모리 대역폭 요구가 커서 소자·공정·패키징의 최적화가 동시에 필요합니다.

핵심 지표 예시

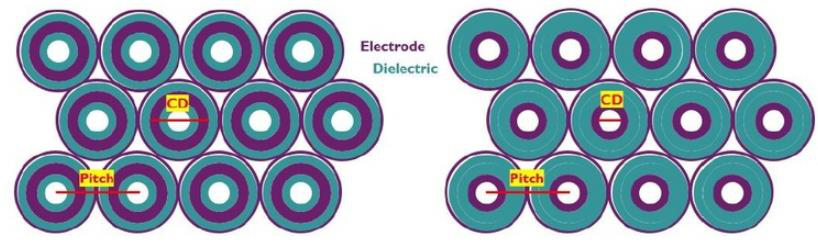

섹션 제목: “핵심 지표 예시”미세화 공정에서 **CD(Critical Dimension)**와 Pitch는 성능/수율을 좌우하는 대표 지표입니다.

더 공부하기

섹션 제목: “더 공부하기”- IEEE IRDS: International Roadmap for Devices and Systems

https://irds.ieee.org/ - SEMI: 200mm/300mm Fab Equipment Investment Outlook

https://www.semi.org/en/news-resources/press/semi-worldwide-200mm-fab-equipment-investments-expected-to-reach-25-billion-300mm-fab