DRAM

DRAM은 1T1C 구조를 기반으로 하는 대표적인 휘발성 메모리입니다. 셀 구조와 리프레시 메커니즘을 이해하는 것이 핵심입니다.

DRAM 셀 구조

섹션 제목: “DRAM 셀 구조”트랜지스터 1개와 커패시터 1개로 구성됩니다. 커패시터에 저장된 전하가 데이터이며 시간이 지나면 누설되기 때문에 리프레시가 필요합니다.

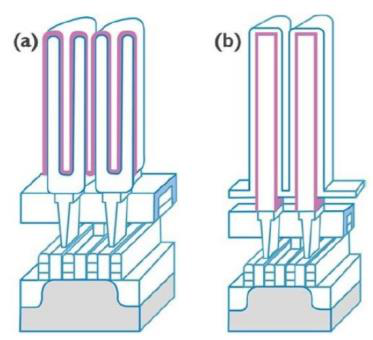

DRAM은 커패시터+트랜지스터 셀 구조 때문에 고집적화가 가능하지만,

누설/변동성 관리가 곧 수율과 성능으로 이어집니다.

DRAM 셀은 작아질수록 커패시터 용량 확보가 어려워집니다.

따라서 고유전율 재료와 3D 구조의 커패시터 설계가 중요합니다.

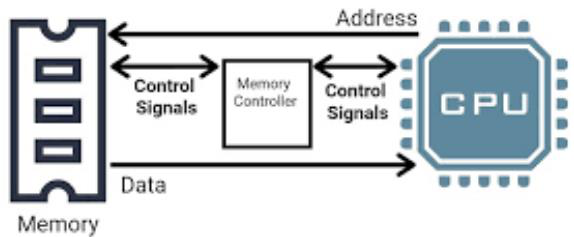

동작 원리

섹션 제목: “동작 원리”- Write: 커패시터 충/방전

- Read: 센스 앰프가 미세 전압을 증폭

- Refresh: 주기적 데이터 복구

리프레시는 셀 누설과 데이터 보존 시간(Retention Time)을 직접 반영합니다.

온도/공정 변동이 리프레시 주기를 결정합니다.

공정/스케일링 이슈

섹션 제목: “공정/스케일링 이슈”- 커패시터 용량 확보(높은 유전율 재료 필요)

- 누설 전류와 소자 변동성 관리

미세화가 진행될수록 셀 간 간섭과 노이즈 마진 감소가 문제로 부각됩니다.

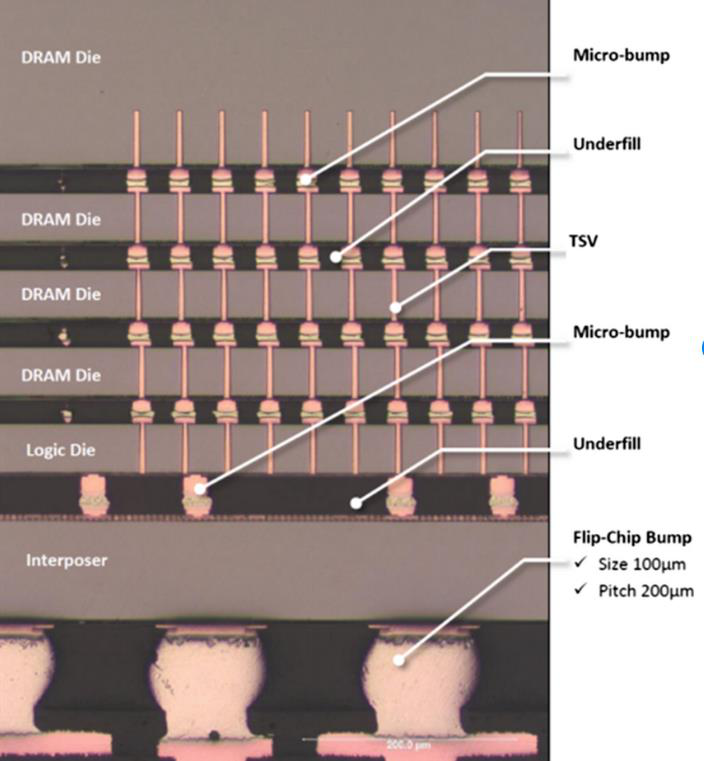

제품 관점: HBM과 LPDDR

섹션 제목: “제품 관점: HBM과 LPDDR”DRAM은 서버/AI용 HBM, 모바일용 LPDDR로 세분화되며,

각 제품은 대역폭/전력/집적도의 우선순위가 다릅니다.

HBM은 적층·마이크로범프·TSV 등 패키징 기술과 함께 발전하며,

AI/HPC에서는 대역폭과 전력 효율이 핵심 경쟁력입니다.

DRAM 제품 스펙을 읽는 법

섹션 제목: “DRAM 제품 스펙을 읽는 법”- 데이터 전송 속도(MT/s): 시스템 대역폭과 직결

- 전압/전력 효율: 모바일/서버 전력 한계에 민감

- 용량/구성: DIMM/패키지 구성과 연동

시장 관점

섹션 제목: “시장 관점”DRAM은 수요/공급 변화에 민감한 시장입니다.

특히 데이터센터/AI 수요가 늘어날수록 대역폭과 전력 효율이 중요한 경쟁 요소가 됩니다.

더 공부하기

섹션 제목: “더 공부하기”- Samsung: HBM3E 12H DRAM 발표

https://news.samsung.com/global/samsung-develops-industry-first-36gb-hbm3e-12h-dram - Micron: DDR5 DRAM 제품 개요

https://www.micron.com/products/dram/ddr5-sdram