회로 기초

회로 기초는 소자 구조를 이해하는 출발점입니다. 전기적 특성이 어떻게 만들어지고, 그 특성이 회로 동작으로 이어지는지 연결하는 것이 핵심입니다.

전기적 기본 개념

섹션 제목: “전기적 기본 개념”- 전압/전류/저항/캐패시턴스/인덕턴스

- KCL/KVL과 선형 회로 해석

- RC·RLC의 시간 상수와 주파수 응답

회로 해석은 “에너지 저장(커패시터·인덕터) + 소모(저항)” 관점으로 보면 직관이 생깁니다.

RC는 지연, RLC는 공진과 안정성을 좌우합니다.

소자와 회로의 연결

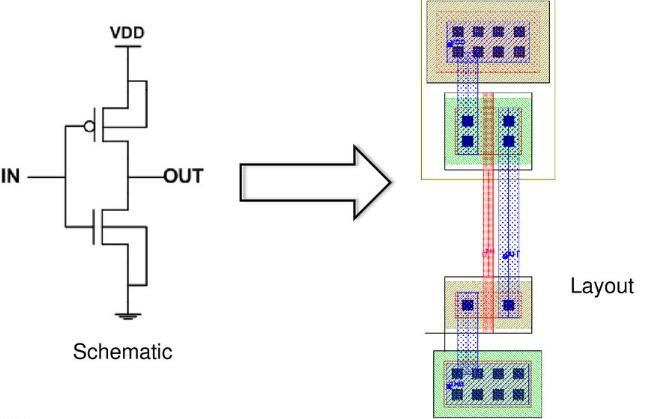

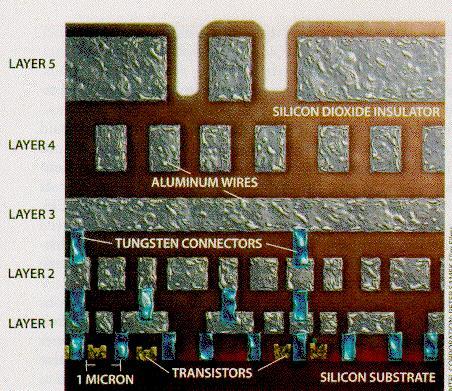

섹션 제목: “소자와 회로의 연결”MOSFET, 다이오드, 커패시터는 모두 공정에서 만들어지는 물리 구조입니다.

회로 성능은 소자의 이동도/누설/임계전압에 따라 달라집니다.

**회로도(Schematic) → 레이아웃(Layout)**로 옮기는 순간, 면적/배선/기생이 성능을 결정합니다.

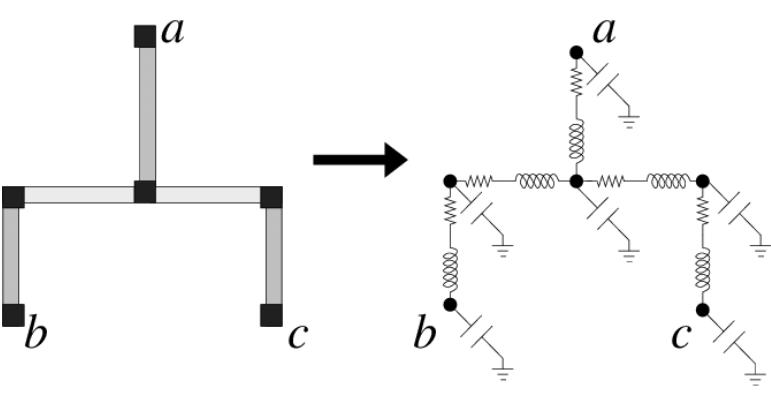

인터커넥트와 기생 성분

섹션 제목: “인터커넥트와 기생 성분”배선 저항과 기생 캐패시턴스는 지연(delay)과 전력 소모를 결정합니다. 공정 미세화가 진행될수록 인터커넥트가 성능 병목이 되는 이유입니다.

배선이 길어질수록 RC 지연이 커지고, 이는 클럭 속도와 전력을 직접 제한합니다.

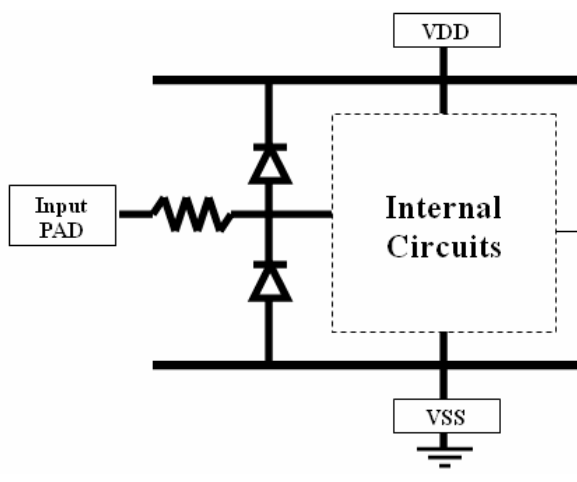

전원/입출력/ESD 기본

섹션 제목: “전원/입출력/ESD 기본”칩 외부와 연결되는 I/O 패드는 전원·신호·ESD 보호가 한 셋으로 설계됩니다.

ESD는 작은 구조 하나로도 칩의 생존 여부를 결정합니다.

설계 시 고려사항

섹션 제목: “설계 시 고려사항”- 타이밍/전력/면적(PPA) 트레이드오프

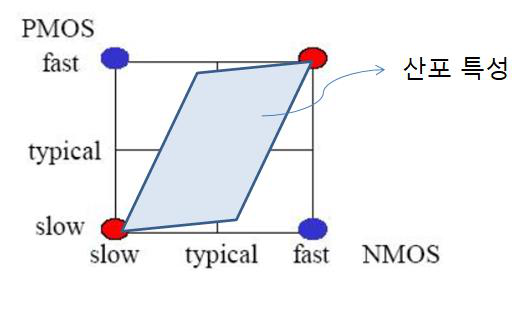

- 공정 변동성(variation)과 수율

회로 설계는 결국 물리적 공정 한계와 논리적 요구사항의 타협입니다.

더 공부하기

섹션 제목: “더 공부하기”- MIT OCW: Circuits and Electronics (6.002)

https://ocw.mit.edu/courses/6-002-circuits-and-electronics-spring-2007/ - MIT OCW: Microelectronic Devices and Circuits (6.012)

https://ocw.mit.edu/courses/6-012-microelectronic-devices-and-circuits-fall-2009/ - MIT OCW: 6.002 강의 영상(유튜브)

https://www.youtube.com/watch?v=2SwT6JnfCq8