MOSFET

MOSFET은 반도체 소자의 중심입니다. 구조와 동작 원리를 이해하면 공정 조건 → 소자 특성 → 회로 성능이 어떻게 연결되는지 한 번에 잡을 수 있습니다.

구조와 기본 동작

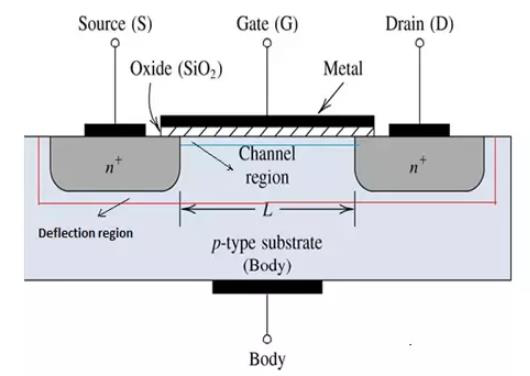

섹션 제목: “구조와 기본 동작”MOSFET은 게이트 전압으로 채널을 형성해 전류를 제어합니다. 이때 산화막 두께, 게이트 길이, 도핑 농도, 채널 재료가 전기적 특성을 좌우합니다.

위 단면에서 게이트(G), 소스(S), 드레인(D), 채널이 전기장에 의해 연결됩니다.

채널이 형성되는 임계 전압(Vt)은 게이트 산화막의 품질과 채널 도핑에 크게 좌우됩니다.

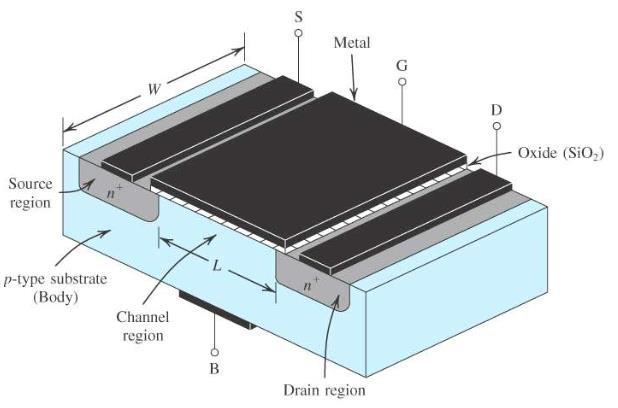

3D 관점에서 보면, 게이트가 채널을 얼마나 둘러싸고 제어하느냐가 누설 전류와 스위칭 성능을 결정합니다.

이 제어력이 부족하면 짧은 채널 효과가 커지고, 결국 전력/성능 모두가 악화됩니다.

핵심 전기적 파라미터

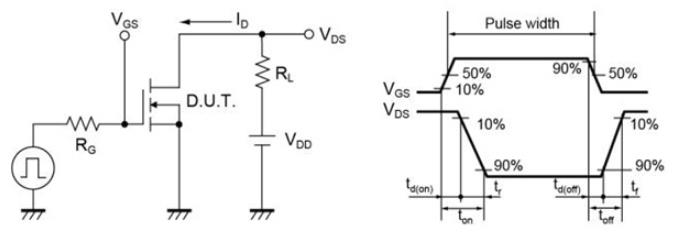

섹션 제목: “핵심 전기적 파라미터”MOSFET의 전기적 특성은 측정 파라미터로 요약할 수 있습니다.

- 임계전압(Vt): 채널이 형성되는 시작점

- 드레인 전류(Id): 스위칭 속도와 직접 연결

- 서브스레시홀드 기울기(SS): 저전력/누설 전류의 핵심 지표

측정 조건(바이어스, 펄스 폭, 온도)이 달라지면 Id–Vg 곡선과 누설 특성이 크게 바뀝니다.

따라서 MOSFET의 “좋음/나쁨”은 단순 수치가 아니라 측정 조건과 함께 해석되어야 합니다.

게이트 산화막과 표면 상태

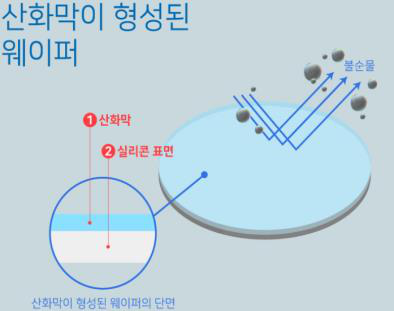

섹션 제목: “게이트 산화막과 표면 상태”MOSFET은 이름 그대로 Metal–Oxide–Semiconductor 구조입니다.

게이트 산화막의 두께/결함/인터페이스 상태는 Vt, 누설, 신뢰성의 핵심 원인입니다.

산화막이 균일하지 않거나 표면 결함이 많으면 산화막 트랩/고정 전하가 증가합니다.

이 전하들은 게이트 전기장을 왜곡해 Vt 변동과 신뢰성 저하를 유발합니다.

스케일링과 최신 구조

섹션 제목: “스케일링과 최신 구조”미세화가 진행될수록 채널 길이가 짧아져 **짧은 채널 효과(SCE)**와 누설 전류가 급격히 늘어납니다.

이 문제를 해결하기 위해 게이트 제어력을 극대화한 구조가 도입됩니다.

- Planar MOSFET → FinFET → GAA로 구조가 진화

- GAA는 채널을 완전히 감싸 누설 전류를 줄이고 전력/성능 균형을 개선

더 공부하기

섹션 제목: “더 공부하기”- MIT OCW 6.720J: MOSFET C–V/소신호 특성 강의 노트

https://ocw.mit.edu/courses/6-720j-integrated-microelectronic-devices-spring-2007/resources/lecture27/ - MIT OCW 6.777J: MOSFET 강의 노트

https://ocw.mit.edu/courses/6-777j-design-and-fabrication-of-microelectromechanical-devices-spring-2007/resources/07lecture07e/ - MDPI Electronics (2022): GAA Nanosheet FET 공정 리뷰

https://www.mdpi.com/2079-9292/11/21/3589 - MDPI Micromachines (2024): GAA Nanosheet 신뢰성 리뷰

https://www.mdpi.com/2072-666X/15/2/269 - MDPI Nanomaterials (2022): 5nm 이후 GAA 스케일링 리뷰

https://www.mdpi.com/2079-4991/12/10/1739 - MIT AI Hardware Program: Road to Gate-All-Around CMOS

https://www.aihardware.mit.edu/the-road-to-gate-all-around-cmos/ - NPTEL (IIT Delhi): Active Circuit Elements—MOSFET 강의

https://www.youtube.com/watch?v=Tl6nET3FqVo - NPTEL (IIT Kharagpur): Revisiting MOSFET 강의

https://www.youtube.com/watch?v=Z6uBRZPUuDQ - UCLA CMOS Research Lab

https://www.seas.ucla.edu/cmoslab/research.html - National Instruments: MOSFETs 온라인 랩

https://education.ni.com/teach/resources/932/mosfets